Industry Challenges

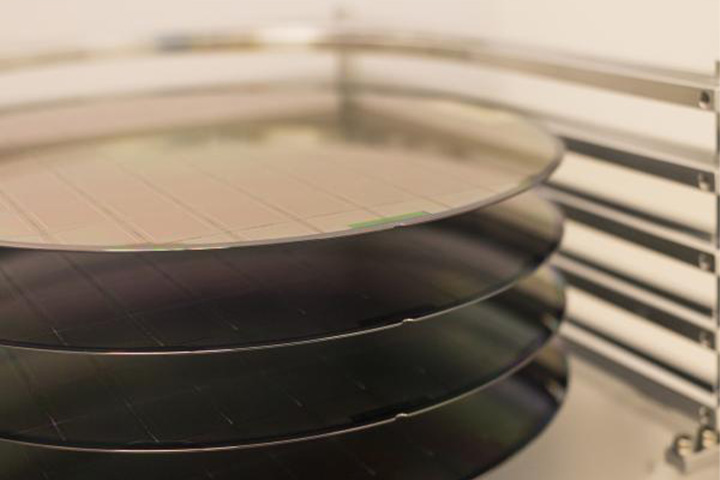

The photovoltaic industry is shifting toward larger wafers (M10, G12) and thinner substrates — a combination that pushes conventional slicing to its limits.

Breakage Risk

Thin wafers are prone to edge chipping and micro-cracks.

TTV Control

Maintaining thickness uniformity on larger formats.

Wire Bow

Tension stability during extended cutting.

Material Loss

Kerf waste directly impacts ingot yield.

Our Methodology: Solving the Precision-to-Yield Equation

We don’t just provide equipment; we deliver a stabilized slicing process. In the transition to thinner wafers and larger formats, our methodology focuses on controlling the physical variables that dictate your final yield.

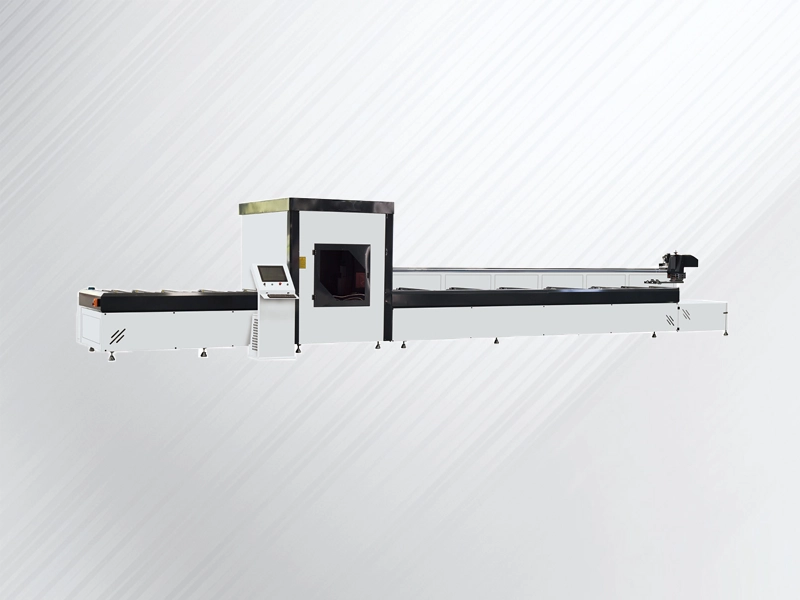

Targeted Cutting Solutions for Photovoltaic Materials

In the PV industry, the material defines the process. We provide specialized slicing and squaring logic designed to handle the unique physical properties of silicon, ensuring your production line achieves maximum yield with minimal kerf loss.

The journey to a high-efficiency cell starts with the Silicon Ingot. Our solution for ingot preparation focuses on geometric precision and surface integrity.

-

The Logic: By optimizing the diamond wire path during squaring, we ensure perfectly perpendicular faces and high dimensional accuracy (±0.1mm).

-

The Benefit: This precision reduces the material allowance needed for the next stage, maximizing the usable volume of the ingot and ensuring a stable foundation for high-speed wafering.

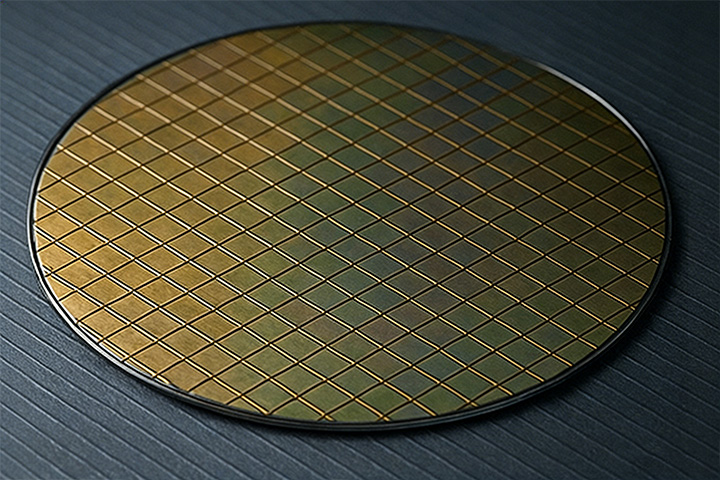

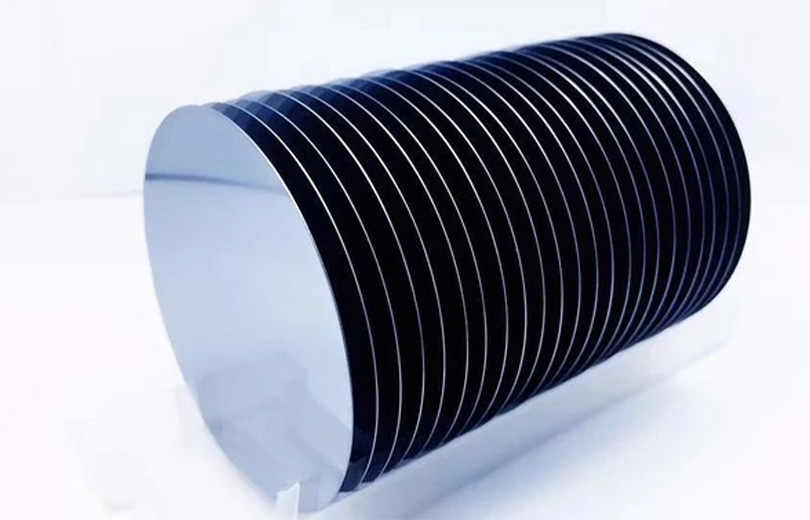

Single-crystal silicon is the backbone of high-efficiency N-type and TOPCon cells, but its brittle nature makes it prone to breakage during thin-wafer slicing.

-

The Logic: Our methodology centers on vibration-dampened slicing. We synchronize wire tension with adaptive feed rates to handle the transition to 100μm wafers.

-

The Benefit: By minimizing the mechanical stress on the crystal lattice, we significantly reduce micro-cracks and edge chipping, directly improving your final “A-grade” wafer yield.

The quality of a Solar Cell Material isn’t just about its thickness; it’s about the texture left behind by the cut. Downstream texturing and etching processes require a uniform surface.

-

The Logic: We utilize a controlled cooling and lubrication process to manage the friction between the diamond wire and the silicon. This prevents “saw marks” and maintains a consistent surface roughness of Ra≤0.2μm.

-

The Benefit: A smoother, more uniform surface simplifies the chemical treatment in cell manufacturing, leading to better light-trapping capabilities and higher conversion efficiency.

The industry shift toward M10 and G12 formats introduces significant “Wire Bow” challenges due to the longer cutting paths.

-

The Logic: For these large-format Photovoltaic substrates, our solution implements a high-frequency tension compensation loop. This keeps the wire taut and straight across the entire width of the ingot, even during high-linear-speed operation.

-

The Benefit: This stabilizes the TTV (Total Thickness Variation) across the large surface area, ensuring that every wafer—from the edge to the center—meets the strict tolerances required by automated module assembly lines.

Production Workflow

A stabilized, controlled slicing process optimized for high-yield silicon wafer production.

Ingot Preparation

Material inspection for internal stress to ensure stability during ultra-thin slicing.

Squaring & Bricking

Defining geometric foundation with dimensional accuracy of ±0.1mm.

Mounting & Alignment

Synchronizing high-frequency tension feedback with feed rates to mitigate micro-cracks.

High-Efficiency Slicing

Vibration-managed process for 100μm – 130μm wafers with Ra ≤ 0.2μm surface.

Cleaning & Inspection

Automated ultrasonic cleaning and TTV/Warp verification for “A-grade” substrates.